No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.2

# **SQ7705 Brief Datasheet V1.2**

Page: 1/534

iMO reserves the right to change the information in this document without prior notice. Please contact iMO to obtain the latest version of product specification before placing your order. Use of iMO devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMO from any and all damages, claims, suits or expenses resulting from such use.

Version: V1.2 No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet

# SQ7705, 16-bit Low Power Secure MCU 64K Bytes Flash, 8K Bytes EEPROM, 8K Bytes SRAM, ADC, AES, SHA, Secure Boot

#### **Features**

- Max. System Frequency 48 MHz

- Instruction Set is Compatible with Toshiba TLCS-870/C1

- Operating Voltage: 2.0V ~ 5.5V

- Operating Temperature: -40°C ~ 85°C

- Deep Sleep Mode Current < 1uA

#### **Memory Configuration**

- SRAM 8K Bytes

- Flash 64K Bytes (512bytes / sector)

- EEPROM 8K Bytes (32bytes / sector)

- EEPROM and Code Flash support dual operation

#### Low voltage detection (LVD) system

#### Brown-out reset detection (BROR)

#### **Clock Source**

- External High Frequency Crystal: 1~16 MHz

- External Low Frequency Crystal: 32.768 KHz

- System Frequency Up to 48MHz (via PLL)

- Internal Low Frequency Oscillator: 32KHz

#### Timer/Counter

- Three 16-bit Timer (TCA), with timer mode, external trigger timer mode, pulse width measurement mode, PPG mode.

- Six 8/16-bit Timer(Timer A), complementary PWM output with dead time

- Real-time Clock (RTC)

- Time Base Timer (TBT)

- Watchdog Timer (WDT)

- System Timer (STM)

- Divider Output (DVO)

### 1/0

- 53 I/O for 64pin Package

- 8 external interrupt input (EINT0~EINT7)

- 16 Key-on Wakeup (KWI0~KWI 15)

#### Package Type

- LQFP 64 (10x10)

- QFN 40 (5x5)

# 12-bit ADC

- 16 CH ADC input

- ADC Vref

#### **DMA**

4CH for Performance Demanding Applications

#### **Peripherals**

- 1 set Low Energy UART

- 3 sets UART

- 2 sets I2C (max. 400KHz)

- 2 sets SPI (max. 10MHz)

#### Hardware Accelerated Symmetric Crypto Engine

- SHA2-256 Hash Engine

- AES-128/AES-256 (ECB, CBC, CFB, CTR, OFB) with Side **Channel Attack Countermeasures**

- Up to 2.9Mbps hardware AES engine which is useful for real-time voice and audio encrypt/decrypt

#### **NIST CAVP Certified Cryptographic Algorithms**

- DRBG (SP800-90A)

- TRNG (SP800-22 Compliant)

- AES-128/AES-256 (FIPS 197)

- SHA-256 (FIPS 180-4)

### Hardware-isolated, Secure Execution Environment

- Support Secure Zone and Secure Peripherals

- Support Secure Bootloader and Anti-Tamper

- Secure Memory (SRAM, Flash, EEPROM)

### NIST FIPS 140-3 compliant tamper-resistant technology

#### **Applications**

- Smart Home, Smart Lock,

- **BMS System**

- Wireless Node Device

- **IoT Application**

Page: 2/534

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

| 1. PREFACE                                            | 4  |

|-------------------------------------------------------|----|

| 2. PRODUCT OVERVIEW                                   | 6  |

| 2.1 Block Diagram                                     |    |

| 2.2 PIN ASSIGNMENT/ DESCRIPTION                       | 7  |

| 2.3 I/O CIRCUIT TYPE                                  |    |

| 3. ELECTRICAL CHARACTERISTICS                         | 24 |

| 3.1 Absolute Maximum Rating                           | 24 |

| 3.2 OPERATION CONDITIONS                              |    |

| 3.2.1 Operation Conditions                            |    |

| 3.2.2 Clock Timing                                    |    |

| 3.2.3 I/O Characteristics                             | 26 |

| 3.3 D.C. Characteristics                              |    |

| 3.4 Power-on Reset Characteristics                    |    |

| 3.5 BROR CHARACTERISTICS                              |    |

| 3.6 LVD CHARACTERISTICS                               |    |

| 3.7 ADC CHARACTERISTICS                               |    |

| 3.8 Flash Characteristics                             |    |

| 3.9 EEPROM CHARACTERISTICS                            |    |

| APPENDIX A. PRODUCT NUMBER INFORMATION                |    |

| APPENDIX B. PACKAGE INFORMATION                       |    |

| APPENDIX C. IMQ IDE SUPPORTS ADM MODE AND USER MODE   |    |

| I. ESTABLISHMENT AND RESOURCE PLANNING OF ADM PROJECT |    |

| II. USER Project Creation and Resource Viewing        |    |

| III. ADM MODE SECURE SRAM                             |    |

| IV. USER MODE SECURE SRAM                             |    |

| V. ADM AND USER MODE SHARE SRAM                       |    |

| VI. USER AND ADM MODE SWITCH                          |    |

| VII. OTHERS                                           |    |

| APPENDIX D. TABLE OF TERMINOLOGY ABBREVIATION         | 44 |

| REVISION HISTORY                                      | 47 |

No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.2

#### **Preface** 1.

SQ7705 has a maximum operating frequency of 48MHz, has 64KB Flash, 8KB EEPROM, 8KB SRAM, supporting secure storage. Providing hardware AES-128/AES-256 and SHA-256 engines, and side-channel attack protection and tamper detection. It has a 12-bit ADC, high-precision internal high-frequency oscillator (±1.5%, -20~70°C) and precise low-voltage detection (LVD), and consumes <1.2uA in deep sleep mode. Rich peripherals: 3 16-bit timers (with counter, external trigger, PWM, PPG), 3 8/16-bit timers (with dead-zone complementary PWM output), 3 sets of UART, 1 set of low-power UART, 2 sets of I2C, 2 sets of SPI, RTC with perpetual calendar function, wake-up and interrupt functions. With a variety of internal and external clock sources, users can optimize and adjust the working mode according to different needs such as performance and power consumption.

SQ7705 uses the 870E core and is compatible with the TLCS-870/C1 instruction set architecture. It is a powerefficient and low-gate-count computing core. Its variable-length instruction set provides 38 sets of core instructions, 9 addressing modes, and the instruction opcode length. From 1 to 5 digits, most general instructions are 2 to 4 digits.

The core is a three-stage pipeline design. The instruction queue and core functional units can frequently execute instructions in a single cycle. The Harvard architecture allows the system to fetch instructions and access data at the same time. Specific hardware is specially designed to handle instruction and data alignment to improve work efficiency.

A variety of internal and external clock sources can be selected according to the frequency required by the user, and can also support digital peripherals and precise analog features. Users can optimize and adjust the working mode according to different needs such as performance and power consumption.

Note: In 8KB EEPROM, 7.5K Bytes are for customer configuration; 0.5K Bytes are for MCU internal use.

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

| Product No.                       | SQ7705LA064SGGR                                                      | SQ7705N5040SGGR                                                      |

|-----------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|

| Pins/ (IOs)                       | 64 / (53)                                                            | 40/ (53)                                                             |

| Operating Voltage                 | 2.0~5.5V                                                             | 2.0~5.5V                                                             |

| Operating Temp.                   | -40~85°C                                                             | -40~85°C                                                             |

| External Interrupt                | 16                                                                   | 16                                                                   |

| Flash                             | 64K Bytes                                                            | 64K Bytes                                                            |

| EEPROM                            | 8K Bytes                                                             | 8K Bytes                                                             |

| RAM                               | 8K Bytes                                                             | 8K Bytes                                                             |

| ADC                               | 12-bit x16-CH<br>(VDD, External)                                     | 12-bit x16-CH<br>(VDD, External)                                     |

| Interrupt                         | External : 8<br>Internal : 44                                        | External : 8<br>Internal : 44                                        |

| Internal Oscillator /<br>Accuracy | 48MHz<br>+/- 1% @ 0~50°C<br>+/- 1.5% @ -20~70°C<br>+/- 3% @ -40~85°C | 48MHz<br>+/- 1% @ 0~50°C<br>+/- 1.5% @ -20~70°C<br>+/- 3% @ -40~85°C |

| External Crystal                  | 1~16MHz ,32768Hz                                                     | 1~16MHz ,32768Hz                                                     |

| BROR                              | 1 Level                                                              | 1 Level                                                              |

| LVD                               | 8 Levels<br>(+/- 3%)*2                                               | 8 Levels<br>(+/- 3%)*2                                               |

|                                   | 8/16-bit Timer A x 3                                                 | 8/16-bit Timer A x 3                                                 |

| Timer /<br>Counter                | 16-bit TCA x 3                                                       | 16-bit TCA x 3                                                       |

|                                   | WDT,TBT,RTC,STM                                                      | WDT,TBT,RTC,STM                                                      |

| PWM/PPG                           | 8/16-bit Timer A x 3                                                 | 8/16-bit Timer A x 3                                                 |

| 1 11111111                        | 16-bit TCA x 3                                                       | 16-bit TCA x 3                                                       |

| Communication                     | LEUART x 1<br>UART x 3<br>SPI x 2<br>I2C x 2                         | LEUART x 1<br>UART x 3<br>SPI x 2<br>I2C x 2                         |

| OCDE                              | Yes                                                                  | Yes                                                                  |

| Package Type                      | LQFP64(10x10)                                                        | QFN40(5x5)                                                           |

Note 1:" VDD" means using VDD as internal reference voltage; "external" means there is on external reference voltage Note 2: SQ series products have 8-level LVD, with a minimum accuracy of ±3%. For detailed specifications of each level, please refer to the product specification sheet.

Page: 5/534

iMO reserves the right to change the information in this document without prior notice. Please contact iMO to obtain the latest version of product specification before placing your order. Use of iMO devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMO from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

#### 2. **Product Overview**

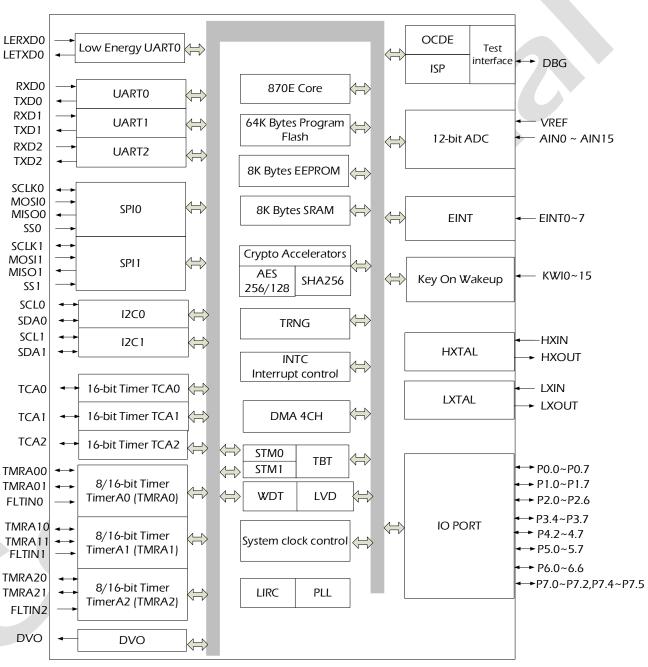

# 2.1 Block Diagram

Figure 2-1 SQ7705 Block Diagram

Note: TimerA (TMRA) is 8/16-bit timer/counter; TMRA00 and TMRA01 are timer/counter input/output function.

Page: 6/534

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.2

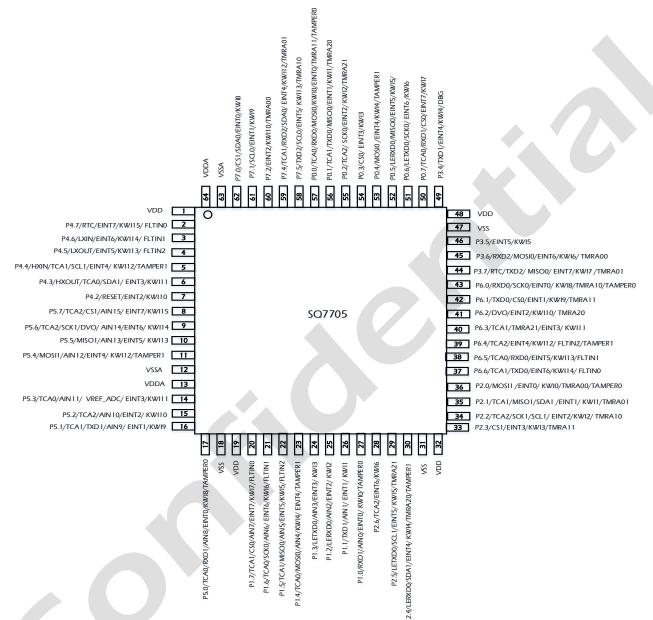

# 2.2 Pin Assignment/ Description

Product No.: SQ7705LA064SGGR (LQFP64 10x10)

Figure 2-2 Pin Assignment of SQ7705 (LQFP-64)

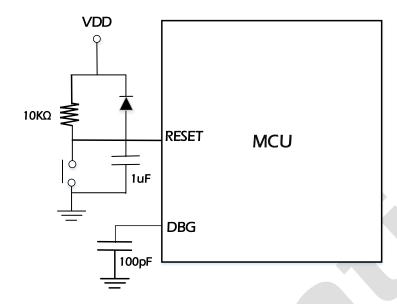

Note 1: SQ7705 simulation needs to connect P3.4/DBG, P4.2/RESET, VDD, and VSS. For the simulation pins reserved by the customer on the system board, please refer to the external reference circuit. It is not recommended to add other components to avoid affecting the simulation characteristics or functions

Note 2: SQ7705 programming is performed by OCDE pins. For the programming pins reserved by the customer on the system board, please refer to the external reference circuit. It is not recommended to add other components to avoid affecting the programming characteristics or Function. 4-wire OCDE pin: Same as the simulation pin (P3.4/DBG, P4.2/RESET, VDD, and VSS). It takes about (7) seconds to burn the 64KByte program space in a single IC. iMO emulator (MO-Link) and writer support this burning mode.

Page: 7/534

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

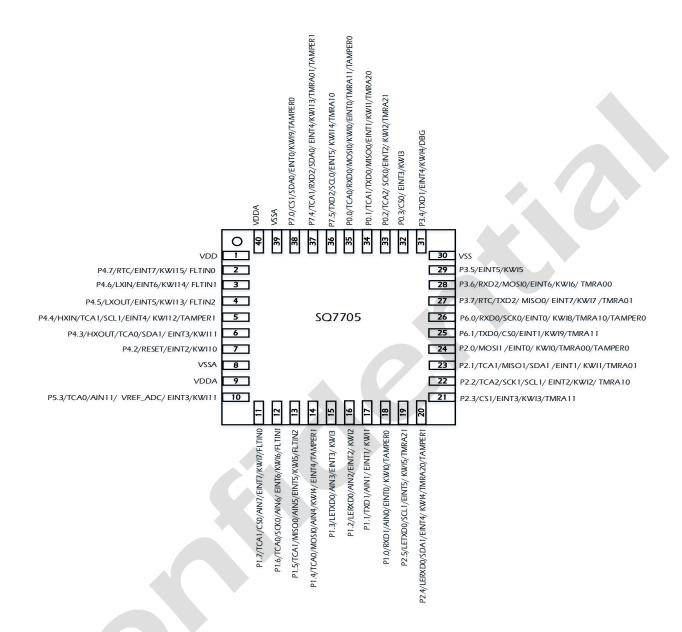

Product No.: SQ7705N5040SGGR (QFN40 5x5)

Figure 2-3 Pin Assignment of SQ7705 (QFN40)

Note 1: SQ7705 simulation needs to connect P3.4/DBG, P4.2/RESET, VDD, and VSS. For the simulation pins reserved by the customer on the system board, please refer to the external reference circuit. It is not recommended to add other components to avoid affecting the simulation characteristics or functions

Note 2: SQ7705 programming is performed by OCDE pins. For the programming pins reserved by the customer on the system board, please refer to the external reference circuit. It is not recommended to add other components to avoid affecting the programming characteristics or Function. 4-wire OCDE pin: Same as the simulation pin (P3.4/DBG, P4.2/RESET, VDD, and VSS). It takes about (7) seconds to burn the 64KByte program space in a single IC. iMQ emulator (MQ-Link) and writer support this burning mode.

Page: 8/534

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

| No.:       | TDDS01-S7705-EN(B) |                          | Name: SQ7705 Brief Datasheet |                 | t Version: V1.2                                                                                                                                                                                                                                                                                                 |

|------------|--------------------|--------------------------|------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 64<br>Pin. | 40<br>Pin          | Pin Name,                | /Pin Option                  | I/O Type        | Function Description                                                                                                                                                                                                                                                                                            |

| 1          | 1                  | VDD                      |                              | Power           | Positive power supply.                                                                                                                                                                                                                                                                                          |

| 2          | 2                  | P4.7/RTC/EINT7/KWI15/ F  | LTIN0                        | I/O<br>(Type A) | P4.7 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistors.  RTC, external interrupt EINT7, wake up pin KWI15, 8/16-bit timer FLTIN0 input are pin-shared with P4.7.                                                                                            |

| 3          | 3                  | P4.6/LXIN/EINT6/KWI14/ I | FLTIN 1                      | I/O<br>(Type B) | P4.6 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistors.  LXIN, external interrupt EINT6, wake up pin  KWI14, 8/16-bit timer FLTIN1 input are pin-shared with P4.6. LXIN is connected to low frequency external crystal.                                     |

| 4          | 4                  | P4.5/LXOUT/EINT5/KWI13   | 3/ FLTIN2                    | I/O<br>(Type B) | P4.5 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistors.  LXOUT, external interrupt EINT5, wake up pin KWI13, 8/16-bit timer FLTIN2 input are pin-shared with P4.5. LXOUT is connected to low frequency external crystal.                                    |

| 5          | 5                  | P4.4/HXIN/TCA1/SCL1/ EII | NT4/ KWI12/TAMPER1           | I/O<br>(Type B) | P4.4 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistors.  HXIN, 16-bit timer TCA1, SCL1 (I2C bus clock input/output), external interrupt EINT4, wake up pin KWI12 and TAMPER1 are pin shared with P4.4.  HXIN is connect to high frequency external crystal. |

| 6          | 6                  | P4.3/HXOUT/TCA0/SDA1/    | ÉINT3/KWI11                  | I/O<br>(Type B) | P4.3 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistors.  HXOUT, 16-bit timer TCA0, SDA1 (I2C bus data input/output), external interrupt EINT3, wake up pin KWI11 are pin-shared with P4.3. HXOUT is connected to high frequency external crystal.           |

Page: 9/534

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

| 7  | 7  | P4.2/RESET/EINT2/KWI10                 | I/O<br>(Type A) | P4.2 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistors.  External interrupt EINT2, wake up pin KWI10 are pin-shared with P4.2.  RESET is pin-shared with P4.2. Reset is low-active.                        |

|----|----|----------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8  |    | P5.7/TCA2/CS1/AIN15/ EINT7/KWI15       | I/O<br>(Type C) | P5.7 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistors.  16-bit timer TCA2, CS1 (SPI chip select), ADC input AIN15, external interrupt EINT7, wake up pin KWI15 are pin-shared with P5.7.                  |

| 9  |    | P5.6/TCA2/SCK1/DVO/ AIN14/EINT6/ KWI14 | I/O<br>(Type C) | P5.6 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistors.  16-bit timer TCA2, SCK1 (SPI clock), divider output (DVO), ADC input AIN14, external interrupt EINT6, wake up pin KWI14 are pin-shared with P5.6. |

| 10 |    | P5.5/MISO1/AIN13/EINT5/ KWI13          | I/O<br>(Type C) | P5.5 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  MISO1 (SPI master in salve out), ADC input AIN13, external interrupt EINT5, wake up pin KWI13 are pin-shared with P5.5.                            |

| 11 |    | P5.4/MOSI1/AIN12/EINT4/ KWI12/TAMPER1  | I/O<br>(Type C) | P5.4 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  MOSI1 (SPI master out slave in), ADC input AIN12, external interrupt EINT4, wake up pin KWI12 and TAMPER1 are pin-shared with P5.4.                |

| 12 | 8  | VSSA                                   | GND             | Analog power ground                                                                                                                                                                                                                                            |

| 13 | 9  | VDDA                                   | Power           | Analog positive power supply.                                                                                                                                                                                                                                  |

| 14 | 10 | P5.3/TCA0/AIN11/ VREF_ADC/EINT3/KWI11  | I/O<br>(Type C) | P5.3 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  16-bit timer TCA0, ADC input AIN11, VREF_ADC, external interrupt EINT3, wake up pin KWI11 are pin-shared with P5.3.                                |

Page: 10/534

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

|    |    | T                                       | 1               | <u>,                                      </u>                                                                                                                                                                                                                                  |

|----|----|-----------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 |    |                                         | I/O<br>(Type C) | P5.2 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  16-bit timer TCA2, ADC input AIN10, external interrupt EINT2, wake up pin KWI10 are pin-shared with P5.2.                                                           |

| 16 |    | P5.1/TCA1/TXD1/AIN9/ EINT1/KWI9         | I/O<br>(Type C) | P5.1 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  16-bit timer TCA1, UART TXD1, ADC input AIN9, external interrupt EINT1, wake up pin KWI9 are pin-shared with P5.1.                                                  |

| 17 |    | P5.0/TCA0/RXD1/AIN8/ EINT0/KWI8/TAMPER0 | I/O<br>(Type C) | P5.0 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  16-bit timer TCA0, UART RXD1, ADC input AIN8, external interrupt EINT0, wake up pin KWI8 and TAMPER0 are pin-shared with P5.0.                                      |

| 18 |    | vss                                     | GND             | Ground                                                                                                                                                                                                                                                                          |

| 19 |    | VDD                                     | Power           | Positive power supply.                                                                                                                                                                                                                                                          |

| 20 | 11 | P1.7/TCA1/CS0/AIN7/EINT7/KWI7/FLTIN0    | I/O<br>(Type C) | P1.7 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  16-bit timer TCA1, CS0 (SPI chip select), ADC input AIN7, external interrupt EINT7, wake up pin KWI7,8/16-bit timer FLTIN0 input are pin-shared with P1.7.          |

| 21 | 12 | P1.6/TCA0/SCK0/AIN6/ EINT6/KWI6/FLTIN1  | I/O<br>(Type C) | P1.6 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  16-bit timer TCA0, SCK0 (SPI clock input/output), ADC input AIN6, external interrupt EINT6, wake up pin KWI6, 8/16-bit timer FLTIN1 input are pin-shared with P1.6. |

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

|    |    |                                          |                 | P1.5 is bi-directional I/O pins, which are software                                                                                                                                                                                                              |

|----|----|------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22 | 13 | P1.5/TCA1/MISO0/AIN5/ EINT5/KWI5/FLTIN2  | I/O<br>(Type C) | configurable to be with pull-up or pull-down resistor.  16-bit timer TCA1, MISOO (SPI master in slave out), ADC input AIN5, external interrupt EINT5, wake up pin KWI5, 8/16-bit timer FLTIN2 input are pin-shared with P1.5.                                    |

| 23 | 14 | P1.4/TCA0/MOSI0/AIN4/ KWI4/EINT4/TAMPER1 | I/O<br>(Type C) | P1.4 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  16-bit timer TCA0, MOSI0 (SPI master out slave in), ADC input AIN4, external interrupt EINT4, wake up pin KWI4 and TAMPER1 are pin-shared with P1.4. |

| 24 | 15 | P1.3/LETXD0/AIN3/EINT3/ KWI3             | I/O<br>(Type C) | P1.3 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  Low energy UART LETXD0, ADC input AIN3, external interrupt EINT3, wake up pin KWI3 are pin-shared with P1.3.                                         |

| 25 | 16 | P1.2/LERXD0/AIN2/EINT2/ KWI2             | I/O<br>(Type C) | P1.2 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  Low energy UART LERXD0, ADC input AIN2, external interrupt EINT2, wake up pin KWI2 are pin-shared with P1.2.                                         |

| 26 | 17 | P1.1/TXD1/AIN1/ EINT1/ KWI1              | I/O<br>(Type C) | P1.1 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  UART TXD1, ADC input AIN1, external interrupt EINT1, wake up pin KWI1 are pin-shared with P1.1.                                                      |

| 27 | 18 | P1.0/RXD1/AIN0/EINT0/ KWI0/TAMPER0       | I/O<br>(Type C) | P1.0 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  UART RXD1, ADC input AIN0, external interrupt EINT0, wake up pin KWI0 and TAMPER0 are pinshared with P1.0.                                           |

| 28 |    | P2.6/TCA2/EINT6/KWI6                     | I/O<br>(Type C) | P2.6 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.                                                                                                                                                       |

Page: 12/534

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.2

|    |    |                                             |                 | 16-bit timer TCA2, external interrupt EINT6, wake up pin KWI6 are pin-shared with P2.6.                                                                                                                                                                                                    |

|----|----|---------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29 | 19 | P2.5/LETXD0/SCL1/EINT5/ KWI5/TMRA21         | I/O<br>(Type C) | P2.5 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  Low energy UART LETXD0, SCL1 (I2C clock input/output), external interrupt EINT5, wake up pin KWI5, 8/16-bit timer TMRA21 are pin-shared with P2.5.                             |

| 30 | 20 | P2.4/LERXD0/SDA1/EINT4/ KWI4/TMRA20/TAMPER1 | I/O<br>(Type C) | P2.4 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  Low energy UART LERXDO, SDA1 (I2C data input/output), external interrupt EINT4, wake up pin KWI4, 8/16-bit timer TMRA20 and TAMPER1 are pin-shared with P2.4.                  |

| 31 |    | VSS                                         | GND             | Ground                                                                                                                                                                                                                                                                                     |

| 32 |    | VDD                                         | Power           | Positive power supply.                                                                                                                                                                                                                                                                     |

| 33 | 21 | P2.3/CS1/EINT3/KWI3/ TMRA11                 | I/O<br>(Type A) | P2.3 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  CS1 (SPI chip select), external interrupt EINT3, wake up pin KWI3, 8/16-bit timer TMRA11 are pinshared with P2.3.                                                              |

| 34 | 22 | P2.2/TCA2/SCK1/SCL1/ EINT2/KWI2/TMRA10      | I/O<br>(Type A) | P2.2 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  16-bit timer TCA2, SCK1 (SPI clock input/output),  SCL1 (I2C clock input/output), external interrupt  EINT2, wake up pin KWI2, 8/16-bit timer TMRA10 are pin-shared with P2.2. |

| 35 | 23 | P2.1/TCA1/MISO1/SDA1/<br>EINT1/ KWI1/TMRA01 | I/O<br>(Type A) | P2.1 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  16-bit timer TCA1, MISO1 (SPI master in slave out), SDA1 (IZC data input/output), external interrupt                                                                           |

Page: 13/534

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.2

| 8/16-bit timer<br>th P2.1.                     |

|------------------------------------------------|

| th P2.1.                                       |

|                                                |

|                                                |

|                                                |

| ins, which are software                        |

| ull-up or pull-down                            |

|                                                |

| ve in), external interrupt                     |

| 8/16-bit timer TMRA00                          |

| red with P2.0.                                 |

| ins, which are software                        |

| ull-up or pull-down                            |

| ,                                              |

| XD0, external interrupt                        |

| 4, 8/16-bit timer FLTIN0                       |

| P6.6.                                          |

| ins, which are software                        |

| ull-up or pull-down                            |

|                                                |

| XD0, external interrupt                        |

| 3, 8/16-bit timer FLTIN1                       |

| P6.5.                                          |

| ins, which are software<br>                    |

| ull-up or pull-down                            |

|                                                |

| Il interrupt EINT4, wake                       |

| ner FLTIN2 and TAMPER1                         |

| P6.4.                                          |

| ins, which are software<br>ull-up or pull-down |

| an-up or pun-down                              |

| ıl interrupt EINT3, wake                       |

| ner TMRA21 are pin-                            |

| ici Tivilo (21 dic pii i                       |

| ins, which are software                        |

| ull-up or pull-down                            |

| 1 1- <del></del>                               |

| nal interrupt EINT2,                           |

| bit timer TMRA20 are                           |

| 2 3 2                                          |

| rii 74 Fii 83 Fii 7 No Fii 7                   |

Page: 14/534

iMO reserves the right to change the information in this document without prior notice. Please contact iMO to obtain the latest version of product specification before placing your order. Use of iMO devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMO from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

|    |    | Т                                       | 1               | T                                                                                                                                                                                                                                                           |

|----|----|-----------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 42 | 25 | P6.1/TXD0/CS0/EINT1/KWI9/TA11           | I/O<br>(Type A) | P6.1 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  UART TXD0, CS0 (SPI chip select), external interrupt EINT1, wake up pin KWI9 are pin-shared with P6.1.                                          |

| 43 | 26 | P6.0/RXD0/SCK0/EINT0/ KWI8/TA10/TAMPER0 | I/O<br>(Type A) | P6.0 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  UART RXD0, SCK0 (SPI clock input/output), external interrupt EINT0, wake up pin KWI8, 8/16-bit timer TA10 and TAMPER0 are pin-shared with P6.0. |

| 44 | 27 | P3.7/RTC/TXD2/ MISO0/ EINT7/KWI7/TA01   | I/O<br>(Type A) | P3.7 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  RTC, UART TXD2, SPI MISO0, external interrupt EINT7, wake up pin KWI 7, 8/16 timer TA01 are pin-shared with P3.7.                               |

| 45 | 28 | P3.6/RXD2/MOSI0/EINT6/KWI6/TA00         | I/O<br>(Type A) | P3.6 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  UART RXD2, SPI MOSIO, external interrupt EINT6, wake up pin KWI6, 8/16 timer TA00 are pin-shared with P3.6.                                     |

| 46 | 29 | P3.5/EINT5/KWI5                         | I/O<br>(Type A) | P3.5 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  External interrupt EINT5, wake up pin KWI5 are pinshared with P3.7.                                                                             |

| 47 | 30 | VSS                                     | GND             | Ground                                                                                                                                                                                                                                                      |

| 48 |    | VDD                                     | Power           | Positive power supply.                                                                                                                                                                                                                                      |

| 49 | 31 | P3.4/TXD1/EINT4/KWI4/DBG                | I/O<br>(Type A) | P3.4 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  UART TXD1, external interrupt EINT4, wake up pin KWI4 are pin-shared with P3.4.                                                                 |

Page: 15/534

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

| 54 | 32 | P0.3/CS0/ EINT3/KWI3           | I/O             | shared with P0.4.  P0.3 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down                                                                                                                                                                            |

|----|----|--------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53 |    | P0.4/MOSI0 /EINT4/KWI4/TAMPER1 | I/O<br>(Type A) | configurable to be with pull-up or pull-down resistor.  MOSIO (SPI master out slave in), external interrupt EINT4, wake up pin KWI4 and TAMPER1 are pin-                                                                                                                                       |

| 52 |    | P0.5/LERXD0/MISO0/EINT5/KWI5/  | I/O<br>(Type A) | P0.5 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  Low energy UART LERXD0, MISO0 (SPI master in slave out), external interrupt EINT5, wake up pin KWI5 are pin-shared with P0.5.  P0.4 is bi-directional I/O pins, which are software |

| 51 |    | P0.6/LETXD0/SCK0/ EINT6 /KWI6  | I/O<br>(Type A) | P0.6 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  Low energy UART LETXDO, SCKO (SPI clock input/output), external interrupt EINT6, wake up pin KWI6 are pin-shared with P0.6.                                                        |

| 50 |    | P0.7/TCA0/RXD1/CS0/EINT7/KWI7  | I/O<br>(Type A) | P0.7 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  16-bit timer TCA0, UART RXD1, CS0 (SPI chip select), external interrupt EINT7, wake up pin KWI7 are pinshared with P0.7.                                                           |

Page: 16/534

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.2

|    |    |                                                      |                 | KWI1, 8/16-bit timer TMRA20 are pin-shared with P0.1.                                                                                                                                                                                                                              |

|----|----|------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |    |                                                      |                 |                                                                                                                                                                                                                                                                                    |

| 57 | 35 | P0.0/TCA0/RXD0/ MOSI0/ EINT0/KWI0<br>/TMRA11/TAMPER0 | I/O<br>(Type A) | P0.0 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  16-bit timer TCA0, UART RXD0, MOSI0 (SPI master out slave in), external interrupt EINT0, wake up pin KWI0, 8/16-bit timer TMRA11 and TAMPER0 are pin-shared with P0.0. |

| 58 | 36 | P7.5/TXD2/SCL0/EINT5/ KWI14/TMRA10                   | I/O<br>(Type A) | P7.5 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  UART TXD2, SCL0 (I2C clock input/output), external interrupt EINT5, wake up pin KWI14,8/16-bit timer TMRA10 are pin-shared with P7.5.                                  |

| 59 | 37 | P7.4/TCA1/RXD2/SDA0/ EINT4/KWI13/TMRA01<br>TAMPER1   | I/O<br>(Type A) | P7.4 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  16-bit timer TCA1, UART RXD2, SDA0 (I2C data input/output), external interrupt EINT4, wake up pin KWI 13, 8/16-bit timer TMRA01 and TAMPER1 are pin-shared with P7.4.  |

| 60 |    | P7.2/EINT2/KWI11/TMRA00                              | I/O<br>(Type A) | P7.2 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  External interrupt EINT2, wake up pin KWI11,8/16-bit timer TMRA00 are pin-shared with P0.1.                                                                            |

| 61 |    | P7.1/SCL0/EINT1/KWI9                                 | I/O<br>(Type A) | P7.1 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  SCLO (I2C clock input/output), external interrupt EINT1, wake up pin KWI9 are pin-shared with P7.1.                                                                    |

| 62 | 38 | P7.0/CS1/SDA0/EINT0/KWI8 TAMPER0                     | I/O<br>(Type A) | P7.0 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistor.  CS1 (SPI chip select), SDA0 (I2C data input/output), external interrupt EINTO, wake up pin KWI8 and TAMPERO are pin-shared with P7.0.                                  |

Page: 17/534

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

| No.: TDDS01-S7705-EN(B) | Name: SQ7705 Brief Datasheet | Version: V1.2 |

|-------------------------|------------------------------|---------------|

|-------------------------|------------------------------|---------------|

| 63 | 39 | VSSA | GND   | Analog power ground           |

|----|----|------|-------|-------------------------------|

| 64 | 40 | VDDA | Power | Analog positive power supply. |

Page: 18/534

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

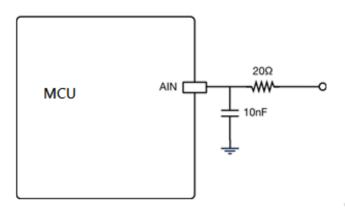

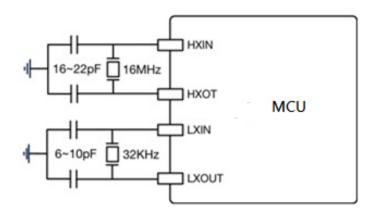

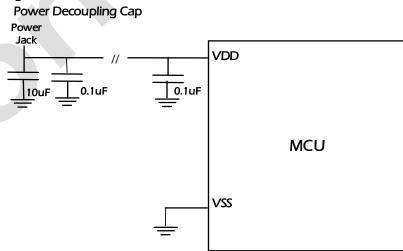

Recommended external application circuits as below figures, please follow the recommendation to design:

### 1. ADC Input Filter:

# **ADC Input Filter**

### 2. External Crystal:

# External Crystal

### 3. Power decoupling:

Note: The 0.1uF near the VDD should be as close as possible to the IC

Page: 19/534

iMO reserves the right to change the information in this document without prior notice. Please contact iMO to obtain the latest version of product specification before placing your order. Use of iMO devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMO from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.2

## 4. RESET and DBG pin:

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

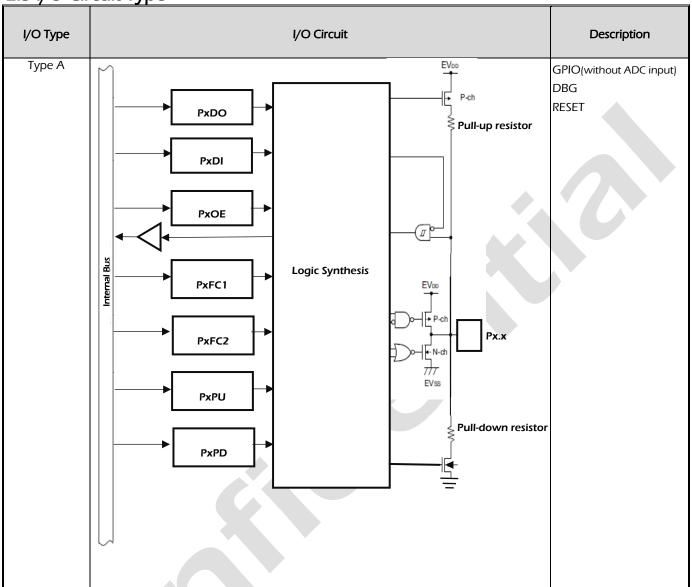

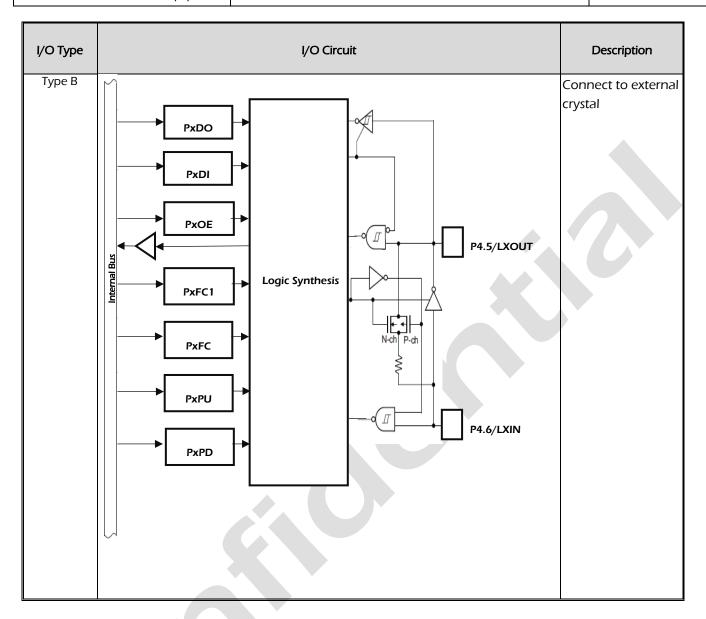

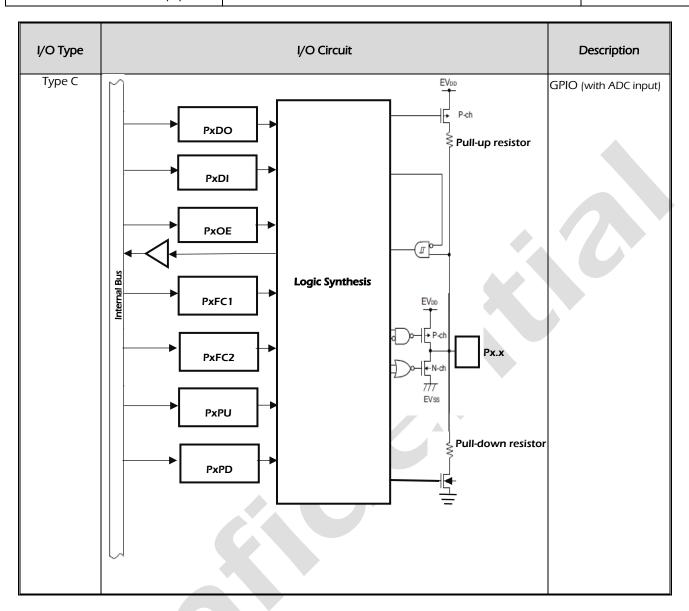

2.3 I/O Circuit Type

Page: 21/534

iMO reserves the right to change the information in this document without prior notice. Please contact iMO to obtain the latest version of product specification before placing your order. Use of iMO devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMO from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

Page: 22/534

iMO reserves the right to change the information in this document without prior notice. Please contact iMO to obtain the latest version of product specification before placing your order. Use of iMO devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMO from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

Page: 23/534

iMO reserves the right to change the information in this document without prior notice. Please contact iMO to obtain the latest version of product specification before placing your order. Use of iMO devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMO from any and all damages, claims, suits or expenses resulting from such use.

| No.: TDDS01-S7705-EN(B) | Name: SQ7705 Brief Datasheet | Version: V1.2 |

|-------------------------|------------------------------|---------------|

|-------------------------|------------------------------|---------------|

#### 3. **Electrical Characteristics**

# 3.1 Absolute Maximum Rating

The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

| $(V_{SS} = 0V$ | ) |

|----------------|---|

|----------------|---|

| Parameter             | Symbol           | Pins         | Ratings         | Unit |

|-----------------------|------------------|--------------|-----------------|------|

| Supply Voltage        | $V_{DD}$         |              | -0.3 to 6.0     | V    |

| Input Voltage         | V <sub>IN</sub>  | All I/O pins | -0.3 to VDD+0.3 | V    |

| Output Current(total) | Іоит             | All I/O pins | 100             | mA   |

| Storage Temperature   | T <sub>STG</sub> | -            | -50 to 125      | °C   |

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

# 3.2 Operation Conditions

The following defines the electrical characteristics of the device when it is operated at voltage and temperature maximum/minimum values. Unless otherwise stated, the standard conditions were determined at "operating temperature 25 ° C and operating voltage VDD = 5 V."

# 3.2.1 Operation Conditions

| Parameter             | Symbol    | Min. | Тур. | Max. | Unit |

|-----------------------|-----------|------|------|------|------|

| Supply Voltage        | $V_{DD}$  | 2.0  | 3.3  | 5.5  | V    |

| Analog Supply Voltage | $V_{DDA}$ | 2.0  | 3.3  | 5.5  | V    |

| Reset Voltage (Note)  | $V_{RST}$ | 1.85 | 1.90 | 1.95 | V    |

| Operating Temperature | Ta        | -40  | 25   | 85   | °C   |

Note: Reset voltage uses BROR

## 3.2.2 Clock Timing

| Parameter                           | Symbol            | Condition                         | Min.   | Тур.  | Max.   | Unit   |

|-------------------------------------|-------------------|-----------------------------------|--------|-------|--------|--------|

| External Clock Source               |                   |                                   |        |       |        |        |

| Low Frequency External Crystal      | f <sub>LXIN</sub> | )-\                               | _      | 32768 | _      | Hz     |

| High Frequency External Crystal     | f <sub>XIN</sub>  | -                                 | 1      | _     | 16     | MHz    |

| Internal Clock Source               |                   |                                   | •      |       | •      |        |

|                                     |                   | $T_A = 25^{\circ}C$               | - 1%   | 48    | + 1%   |        |

| High Frequency Internal Oscillator  |                   | $T_A = 0 \sim 50^{\circ}C$ Note 2 | - 1%   | 48    | + 1%   | MHz    |

| (PLL) <sup>Note1</sup>              | $f_{PLL}$         | T <sub>A</sub> = -20~ 70°C Note 2 | - 1.5% | 48    | + 1.5% | IVITIZ |

|                                     |                   | T <sub>A</sub> = -40~ 85°C        | - 2%   | 48    | + 2%   |        |

| Laur Fragues er Internal Oscillator |                   | T <sub>A</sub> = 25°C             | -15%   | 32    | + 15%  | ld 1-  |

| Low Frequency Internal Oscillator   | f <sub>LIRC</sub> | T <sub>A</sub> = -40~ 85°C        | -30%   | 32    | + 30%  | kHz    |

Note 1: High frequency external crystal (HXIN) can be PLL clock source. When high frequency external crystal (HXIN) is PLL clock source, the external crystal (HXIN) must be 8MHz.

Note 2: The spec is under VDD=  $5V \pm 10\%$  (  $4.5 \sim 5.5V$ ) condition.

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

# 3.2.3 I/O Characteristics

| Parameter           | Symbol              | Condition                         | Min.     | Тур. | Max.     | Unit |

|---------------------|---------------------|-----------------------------------|----------|------|----------|------|

| Input low voltage   | $V_{IL}$            | -                                 | 0        | -    | 0.25 VDD | V    |

| Input high voltage  | V <sub>IH</sub>     | -                                 | 0.75 VDD | -    | VDD      | V    |

| Output low voltage  | V <sub>OL1</sub>    | P0DSEL=0,<br>IOL=2.5mA, VDD=3.3V  | -        | -    | 0.4      | V    |

| Output low voitage  | V <sub>OL2</sub>    | P0DSEL=1,<br>IOL=5mA, VDD=3.3V    | -        | -    | 0.4      | V    |

| Output high voltage | V <sub>OH1</sub>    | PODSEL=0,<br>IOH=0.75mA, VDD=3.3V | VDD-0.6  | -    |          | V    |

| Output High Voltage | V <sub>OH2</sub>    | PODSEL=1,<br>IOH=1.5mA, VDD=3.3V  | VDD-0.6  | -    | -        | ٧    |

|                     |                     | PODSEL=0,<br>Vo=0.1*VDD, VDD=3.3V | 2.5      | 6.7  |          | mA   |

| Output law surrout  | I <sub>OL1</sub>    | PODSEL=0,<br>Vo=0.3*VDD, VDD=3.3V | 7        | 15   |          | mA   |

| Output low current  | ,                   | PODSEL=1,<br>Vo=0.1*VDD, VDD=3.3V | 5        | 13.4 |          | mA   |

|                     | I <sub>OL2</sub>    | P0DSEL=1,<br>Vo=0.3*VDD, VDD=3.3V | 14       | 30   |          | mA   |

|                     | ,                   | PODSEL=0,<br>Vo=0.9*VDD, VDD=3.3V | 74       |      |          | mA   |

| Output high current | I <sub>OH1</sub>    | P0DSEL=0,<br>Vo=0.7*VDD, VDD=3.3V | 3        | 5.8  |          | mA   |

| Output high current | ,                   | P0DSEL=1,<br>Vo=0.9*VDD, VDD=3.3V | 2        | 4.8  | -        | mA   |

|                     | I <sub>OH2</sub>    | P0DSEL=1,<br>Vo=0.7*VDD, VDD=3.3V | 6        | 11.6 |          | mA   |

| Pull-up resistance  | R <sub>PULLUP</sub> | connect to pull-up resistance     | 10       | 20   | 40       | kΩ   |

| Pull-low Resistance | R <sub>PULLDN</sub> | connect to pull-down resistance   | 10       | 20   | 40       | kΩ   |

Note 1: Set PODSEL to select the pin driving force.

No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.2

# 3.3 D.C. Characteristics

| Operating @ 3.3 V · Ta= -40~85°C |                     |                                                                                             |      |      |      |      |  |  |

|----------------------------------|---------------------|---------------------------------------------------------------------------------------------|------|------|------|------|--|--|

| Parameter                        | Symbol              | Condition                                                                                   | Min. | Тур. | Max. | Unit |  |  |

|                                  | I <sub>DD_N0</sub>  | System clock is PLL( clock source is high frequency internal oscillator) fsysclk= PLL 48MHz | _    | 8.2  | -    | mA   |  |  |

| Normal Mode                      | I <sub>DD_N1</sub>  | System clock is HXTAL<br>fsysclk= HXTAL16MHz                                                | _    | 4.1  |      | mA   |  |  |

| (Code executing from Flash)      | I <sub>DD_N2</sub>  | System clock is LIRC<br>fsysclk= LIRC 32KHz                                                 | -    | 1.2  | (-)  | mA   |  |  |

|                                  | I <sub>DD_N3</sub>  | System clock is LXTAL<br>fsysclk= LXTAL 32768Hz                                             | -    | 1.2  | _    | mA   |  |  |

|                                  | I <sub>DD_SL0</sub> | System clock is PLL( clock source is high frequency internal oscillator) fsysclk= PLL 48MHz | -    | 4.6  |      | mA   |  |  |

| Sleep Mode                       | I <sub>DD_SL1</sub> | System clock is HXTAL<br>fsysclk= HXTAL16MHz                                                | 1    | 2.5  |      | mA   |  |  |

| (CPU clock is stopped)           | I <sub>DD_SL2</sub> | System clock is LIRC<br>fsysclk= LIRC 32KHz                                                 | -    | 1.2  |      | mA   |  |  |

|                                  | I <sub>DD_SL3</sub> | System clock is LXTAL<br>fsysclk= LXTAL 32768Hz                                             | _    | 1.2  |      | mA   |  |  |

| Deep Sleep Mode                  | I <sub>DD_DS0</sub> | RTC Disable                                                                                 | _    | 0.6  | _    | uA   |  |  |

| (CPU and RAM are retained)       | I <sub>DD_DS1</sub> | RTC Enable , LXTAL On                                                                       | _    | 0.6  | _    | uA   |  |  |

No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.2

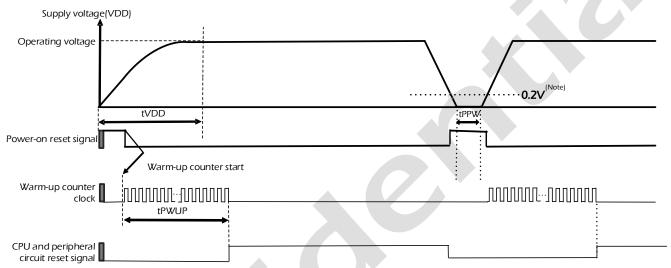

## 3.4 Power-on Reset Characteristics

| Vss=0 · Ta=-40~85 |                                                      |      |      |      |      |  |  |  |  |

|-------------------|------------------------------------------------------|------|------|------|------|--|--|--|--|

| Symbol            | Condition                                            | Min. | Тур. | Max. | Unit |  |  |  |  |

| tPPW              | Power-on reset minimum pulse width                   | 1    | -    | -    | ms   |  |  |  |  |

| tPWUP             | Warming-up time after a reset is clear and CPU ready | -    | 4    | -    | ms   |  |  |  |  |

| tVDD              | Power supply rise time                               | 0.5  |      | 5    | ms   |  |  |  |  |

Note: tPWUP does not include BOOTROM code execution time.

Figure 3-1 Operation Timing of Power-on Reset

Note: In power-down process, the VDD must be 0.2V, then re-power-on to ensure the IC operating normal.

No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.2

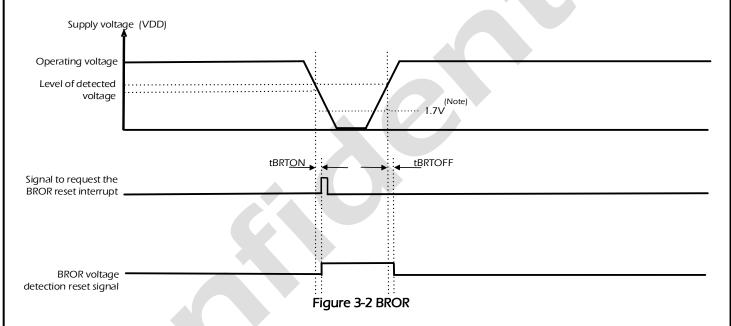

### 3.5 BROR Characteristics

|               |                |                                                                       |      |      | Ta=  | -40~85°C |

|---------------|----------------|-----------------------------------------------------------------------|------|------|------|----------|

| Parameter     | Symbol         | Condition                                                             | Min. | Тур. | Max. | Unit     |

| BROR detected | VBROR_Rising   | VDD rise time and fall time > tVDD<br>(tVDD please refer to ch3.4 POR | 1.95 | 2.0  | 2.05 | V        |

| voltage       | VBROR_ Falling | characteristics )                                                     | 1.85 | 1.90 | 1.95 | V        |

| Symbol  | Description                                    | Min. | Тур. | Max. | Unit |

|---------|------------------------------------------------|------|------|------|------|

| tBRTOFF | BROR voltage detection releasing response time | -    | 1    | 10   | us   |

| tBRTON  | BROR voltage detecting detection response time | -    | 1    | 10   | us   |

Note: Do not perform any operation when VDD under V1.7V. It will cause the operation abnormal.

Page: 29/534

iMO reserves the right to change the information in this document without prior notice. Please contact iMO to obtain the latest version of product specification before placing your order. Use of iMO devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMO from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.2

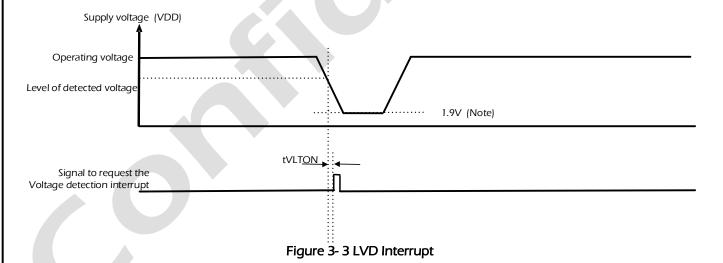

## 3.6 LVD Characteristics

|           |         |                                                       |      |      | Ta=  | -40~85°C |

|-----------|---------|-------------------------------------------------------|------|------|------|----------|

| Parameter | Symbol  | Condition                                             | Min. | Тур. | Max. | Unit     |

|           | VD0LVL1 | Falling Mode ·<br>LVDCR0 <lvdcfg>=000 (Note)</lvdcfg> | 1.90 | 2.00 | 2.10 | V        |

| LVD0      | VD0LVL2 | Falling Mode ·<br>LVDCR0 <lvdcfg>=001</lvdcfg>        | 2.23 | 2.35 | 2.47 | V        |

| LVDO      | VD0LVL3 | Falling Mode ·<br>LVDCR0 <lvdcfg>=010</lvdcfg>        | 2.52 | 2.65 | 2.78 | V        |

|           | VD0LVL4 | Falling Mode ·<br>LVDCR0 <lvdcfg>=011</lvdcfg>        | 2.71 | 2.85 | 2.99 | V        |

|           | VD1LVL1 | Falling Mode ·<br>LVDCR1 <lvdcfg>=100</lvdcfg>        | 2.99 | 3.15 | 3.31 | V        |

| LVD1      | VD1LVL2 | Falling Mode ·<br>LVDCR1 <lvdcfg>=101</lvdcfg>        | 3.78 | 3.98 | 4.18 | V        |

| LVDI      | VD1LVL3 | Falling Mode ·<br>LVDCR1 <lvdcfg>=110</lvdcfg>        | 3.99 | 4.20 | 4.41 | V        |

|           | VD1LVL4 | Falling Mode ·<br>LVDCR1 <lvdcfg>=111</lvdcfg>        | 4.28 | 4.50 | 4.73 | V        |

| Symbol | Description                               | Min. | Тур. | Max. | Unit |

|--------|-------------------------------------------|------|------|------|------|

| tVLTON | Voltage detecting detection response time | -    | 1    | 10   | us   |

Note: When LVD0 is set to VD0LVL1, BROR may be triggered first when the voltage drops.

Page: 30/534

iMO reserves the right to change the information in this document without prior notice. Please contact iMO to obtain the latest version of product specification before placing your order. Use of iMO devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMO from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

# 3.7 ADC Characteristics

VREF ADC=VDD

|                                       |                      | $4.5V \leq VDD \leq 5.5V \cdot T_A = -40$ |          |      |      |

|---------------------------------------|----------------------|-------------------------------------------|----------|------|------|

| Parameter                             | Symbol               | Min.                                      | Тур.     | Max. | Unit |

| Resolution                            | RES <sub>ADC</sub>   | _                                         | 12       | _    | bits |

| Sampling Rate                         | f <sub>ADC</sub>     | _                                         | _        | 470  | KSPS |

| Differential Nonlinearity Error (DNL) | DNL <sub>ADC</sub>   | _                                         | _        | ±2.5 | LSB  |

| Integral Nonlinearity Error (INL)     | INL <sub>ADC</sub>   | _                                         | _        | ±3.5 | LSB  |

| Gain Error                            | E <sub>GAIN</sub>    | _                                         | _        | ±5   | LSB  |

| Offset Error                          | E <sub>OFFSET</sub>  | _                                         | _        | ±4.5 | LSB  |

| Input Voltage Range                   | V <sub>ADC_RNG</sub> | -                                         | -        | VDD  | V    |

| VREF_ADC Voltage Range                | $V_{REF\_ADC}$       |                                           | VDDNote1 |      | V    |

Note 1: VERF\_ADC=VDD, the voltage range 4.5~5.5V

Note 2: Does not include offset and gain compensation

Note 3 : ADC sample rate =  $=\frac{1}{22} \times \frac{fsysclk}{ADCCKDIV}$

Example: When system clock is 24MHz · ADCCKDIV set to 0x02 · ADC Sample rate :  $\frac{1}{22}x\frac{24MHz}{2^2} = 272.727$ ksps

VREF\_ADC=VDD

$2V \le VDD < 4.5V$ ,  $T_A = -40 \sim 85$ °C

|                                       |                     |      | v                  | DD 11.5V 1A | 10 05 0 |

|---------------------------------------|---------------------|------|--------------------|-------------|---------|

| Parameter                             | Symbol              | Min. | Тур.               | Max.        | Unit    |

| Resolution                            | RES <sub>ADC</sub>  | -    | 12                 |             | bits    |

| Sampling Rate                         | f <sub>ADC</sub>    | -    | -                  | 470         | KSPS    |

| Differential Nonlinearity Error (DNL) | DNL <sub>ADC</sub>  | -    | -                  | ±4          | LSB     |

| Integral Nonlinearity Error (INL)     | INL <sub>ADC</sub>  | _    | -                  | ±5          | LSB     |

| Gain Error                            | E <sub>GAIN</sub>   | _    | -                  | ±6          | LSB     |

| Offset Error                          | E <sub>OFFSET</sub> | -    | -                  | ±6          | LSB     |

| Input Voltage Range                   | $V_{ADC\_RNG}$      | _    | _                  | VDD         | V       |

| VREF_ADC Voltage Range                | $V_{REF\_ADC}$      |      | VDD <sup>注 1</sup> |             | V       |

Note 1: VERF\_ADC=VDD, the voltage range  $2\sim5.5V$

Note 2: Does not include offset and gain compensation

Note 3 : ADC sample rate =  $=\frac{1}{22} \times \frac{fsysclk}{ADCCKDIV}$

Example: When system clock is 24MHz · ADCCKDIV set to 0x02 · ADC Sample rate :  $\frac{1}{22}x\frac{24MHz}{2^2} = 272.727$ ksps

Page: 31/534

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.2

# 3.8 Flash Characteristics

$(V_{SS} = 0V, 2.0V \le V_{DD} \le 5.5V, T_{OPR} = -40 \text{ to } 85^{\circ}C)$

| Parameter                                   | Condition                              | Min. | Тур. | Max.    | Unit  |

|---------------------------------------------|----------------------------------------|------|------|---------|-------|

| Number of guaranteed writes to flash memory |                                        | -    | _    | 100,000 | times |

| Flash memory write time                     | Write Time (per byte)                  | _    | _    | 40      | μς    |

|                                             | Chip Erase                             | -    | -    | 40      |       |

| Flash memory erase time                     | Sector Erase<br>(1 sector = 512 bytes) | _    | -    | 5       | ms    |

# 3.9 EEPROM Characteristics

$(V_{SS} = 0V \cdot 2.0V \le V_{DD} \le 5.5V \cdot T_{OPR} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                             | Condition                            | Min. | Тур. | Max.    | Unit  |

|---------------------------------------|--------------------------------------|------|------|---------|-------|

| Number of guaranteed writes to EEPROM |                                      | -    | -    | 100,000 | times |

| EEPROM write time                     | Write Time (per byte)                | _    | ľ    | 40      | μs    |

|                                       | Chip Erase                           |      | _    | 40      |       |

| EEPROM erase time                     | Sector Erase<br>(1 sector =32 bytes) | _    | -    | 5       | ms    |

| iMQ | Techno | logy | Inc |

|-----|--------|------|-----|

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

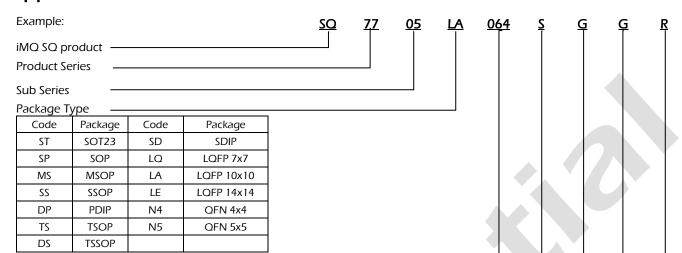

# Appendix A. Product Number Information

#### Pin Count

| Code | Package | Code | Package |

|------|---------|------|---------|

| 005  | 5       | 032  | 32      |

| 006  | 6       | 036  | 36      |

| 800  | 8       | 040  | 40      |

| 010  | 10      | 044  | 44      |

| 014  | 14      | 048  | 48      |

| 016  | 16      | 064  | 64      |

| 020  | 20      | 080  | 80      |

| 024  | 24      | 096  | 96      |

| 028  | 28      | 100  | 100     |

|      |         |      |         |

Program Flash

Data Flash

#### RAM

| Code | Program Flash<br>/Data Flash<br>RAM Size | Code | Program Flash<br>/Data Flash<br>RAM Size |

|------|------------------------------------------|------|------------------------------------------|

| Α    | 128 Bytes                                | Н    | 16K Bytes                                |

| В    | 256 Bytes                                | K    | 24K Bytes                                |

| Е    | 512 Bytes                                | М    | 32K Bytes                                |

| J    | 1K Bytes                                 | N    | 40K Bytes                                |

| L    | 2K Bytes                                 | Р    | 48K Bytes                                |

| T    | 4K Bytes                                 | S    | 64K Bytes                                |

| G    | 8K Bytes                                 | U    | 96K Bytes                                |

| C    | 12K Bytes                                | W    | 128K Bytes                               |

Operating Temp.

| Code | Operating Temp. |

|------|-----------------|

| R    | -40~85°C        |

Page: 33/534

iMO reserves the right to change the information in this document without prior notice. Please contact iMO to obtain the latest version of product specification before placing your order. Use of iMO devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMO from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.2

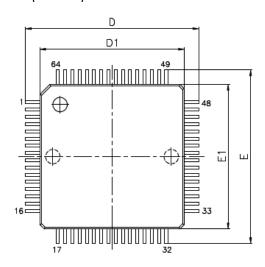

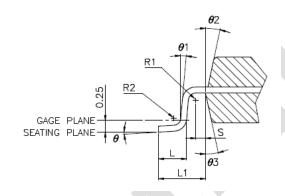

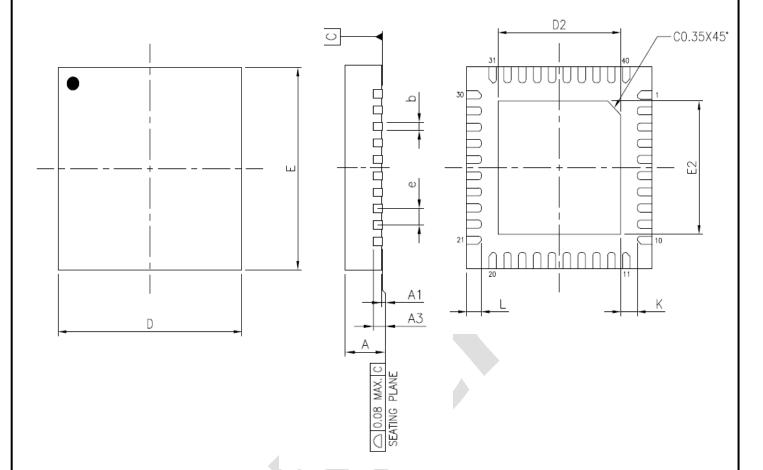

# Appendix B. Package Information

LQFP64 (10x10)

| Cymbol |          | mm      |       |

|--------|----------|---------|-------|

| Symbol | Min.     | Тур.    | Max.  |

| Α      | 1.45     | 1.55    | 1.65  |

| A1     | 0.05     | _       | 0.15  |

| A2     | 1.3      | 1.4     | 1.5   |

| b      | 0.17     | 0.22    | 0.27  |

| c1     | 0.09     | _       | 0.16  |

| D      | 11.75    | 12.00   | 12.25 |

| D1     | 9.90     | 10.00   | 10.10 |

| Е      | 11.75    | 12.00   | 12.25 |

| E1     | 9.90     | 10.00   | 10.10 |

| e      | 0.50 BSC |         |       |

| L      | 0.45     | _       | 0.75  |

| L1     | _        | 1.0 REF | ·     |

Page: 34/534

iMO reserves the right to change the information in this document without prior notice. Please contact iMO to obtain the latest version of product specification before placing your order. Use of iMO devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMO from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.2

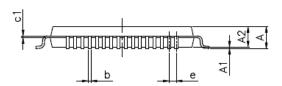

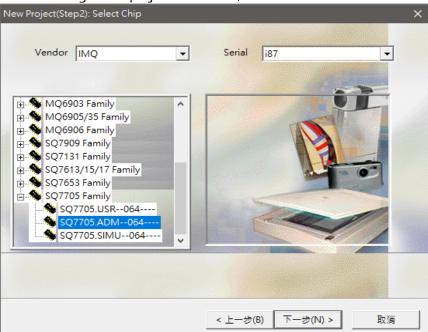

# QFN 40(5x5)

|        |      | mm         |      |  |  |

|--------|------|------------|------|--|--|

| Symbol | Min. | Тур.       | Max. |  |  |

| Α      | 0.70 | 0.75       | 0.80 |  |  |

| A1     | 0.00 | 0.02       | 0.05 |  |  |

| А3     |      | 0.203 REF. |      |  |  |

| b      | 0.15 | 0.20       | 0.25 |  |  |

| D      | 4.90 | 5.00       | 5.10 |  |  |

| Е      | 4.90 | 5.00       | 5.10 |  |  |

| е      |      | 0.40 BSC   |      |  |  |

| K      | 0.20 |            |      |  |  |

| D2     | 3.25 | 3.30       | 3.35 |  |  |

| E2     | 3.25 | 3.30       | 3.35 |  |  |

| L      | 0.35 | 0.40       | 0.45 |  |  |

Page: 35/534

iMO reserves the right to change the information in this document without prior notice. Please contact iMO to obtain the latest version of product specification before placing your order. Use of iMO devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMO from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.2

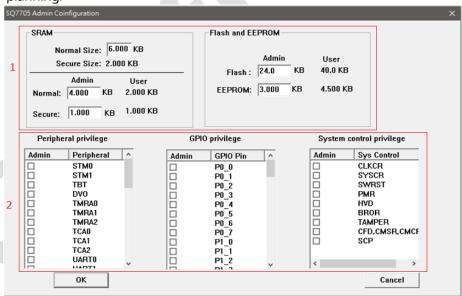

# Appendix C. iMQ IDE Supports ADM Mode and User Mode

i. Establishment and resource planning of ADM project

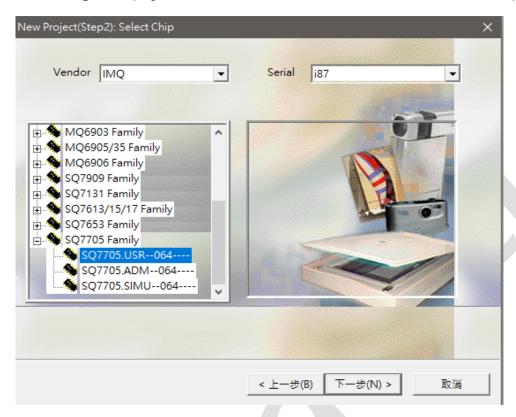

When creating a new project in iMQ IDE, select "SQ7705.ADM-064---" to create an ADM project.

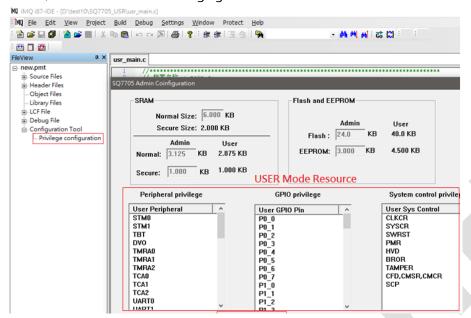

When a new ADM project is created, the "SQ7705 Admin Configuration" window will pop up for resource planning:

In this window, the followings can be planned.

- The size of the SRAM, FLASH and EEPROM areas used by ADM and USER modes.

- Specify whether each peripheral, GPIO, and system control register operate in ADM only or

Page: 36/534

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

ADM/USER mode.

- 3. After pressing "OK," all settings will be saved as a .privCfg file. This file will be used by the ADM project itself and also by the USER mode project.

- 4. ADM projects and USER projects exist in pairs, and the two communicate and coordinate the use of resources through the .privCfg file.

If the processor is to be operated in ADM mode only, all SRAM, EEPROM and FLASH should be allocated to ADM, and all peripheral devices, GPIO and system control registers should be set to ADM Only.

No.: TDDS01-S7705-EN(B) Version: V1.2 Name: SQ7705 Brief Datasheet

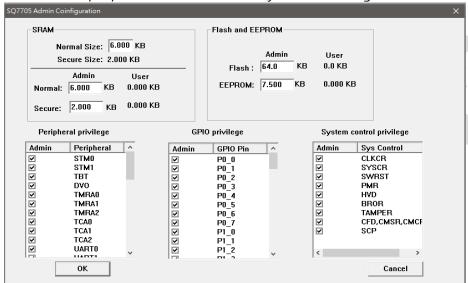

#### ii. **USER Project Creation and Resource Viewing**

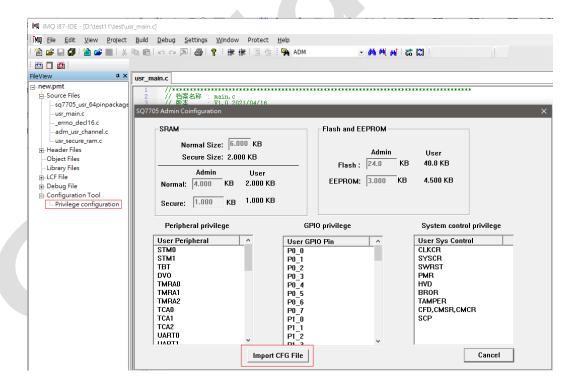

When creating a new project in iMQ IDE, select "SQ7705.USR-064---" to create a USER project.

Resources can't be planned or changed in the USER project, but resources allocated to the USER mode can be viewed.

When creating a new project, the requirement for selecting a .privCfg file will pop up. At this place it is necessary to specify the .privCfg file in the corresponding ADM project (to achieve consistency in resource usage between the ADM and USER projects).

No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.2

Only resources that can be used in USER mode will appear in the list of peripherals, GPIO, and system control, as shown in the following figure:

Whenever the ADM project changes the resource file, the USER project also needs to re-import the new resource file.

To re-select the resource file, double-click "Privilege configuration" in FileView to pop up the resource window, then select "Import CFG File" to import the new resource file.

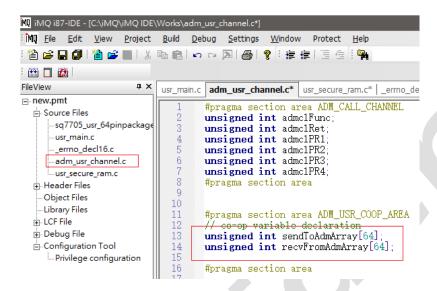

Page: 39/534

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7705-EN(B) Name: SQ7705 Brief Datasheet Version: V1.2

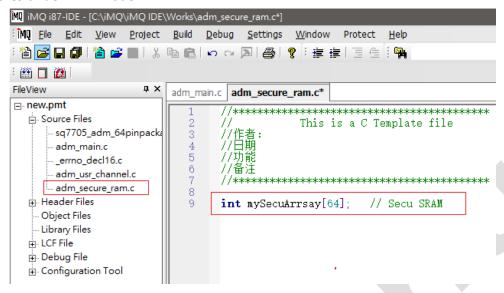

#### iii. ADM MODE SECURE SRAM

Overall variables declared in adm\_secure\_ram.c are automatically allocated in the Secure SRAM address area under ADM mode.

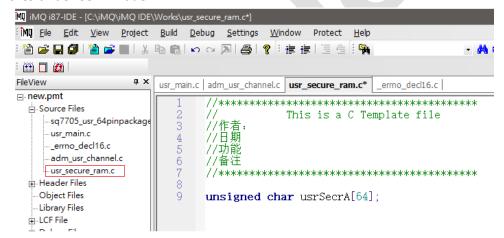

#### **USER MODE SECURE SRAM** iv.

Overall variables declared in usr\_secure\_ram.c will be automatically allocated in the Secure SRAM address area under USER mode.